这学期上VLSI系统设计这门课,同时顺带着把计算机设计与调试的课程设计做了。往FPGA上烧写之前要用Verilog进行仿真,在实验室直接用机房的ModelSim仿真了,但是课下在虚拟机上做有诸多的不便,于是就研究了一下在Mac下写Verilog的方法。

配置Sublime代码高亮

Sublime Text默认是不支持Verilog代码高亮的,可以通过安装插件增加对其的支持。首先要安装Sublime包管理工具,按control+` 打开控制台,并运行以下代码(以Sublime Text 2为例):

1 | import urllib2,os,hashlib; h = '2915d1851351e5ee549c20394736b442' + '8bc59f460fa1548d1514676163dafc88'; pf = 'Package Control.sublime-package'; ipp = sublime.installed_packages_path(); os.makedirs( ipp ) if not os.path.exists(ipp) else None; urllib2.install_opener( urllib2.build_opener( urllib2.ProxyHandler()) ); by = urllib2.urlopen( 'http://packagecontrol.io/' + pf.replace(' ', '%20')).read(); dh = hashlib.sha256(by).hexdigest(); open( os.path.join( ipp, pf), 'wb' ).write(by) if dh == h else None; print('Error validating download (got %s instead of %s), please try manual install' % (dh, h) if dh != h else 'Please restart Sublime Text to finish installation') |

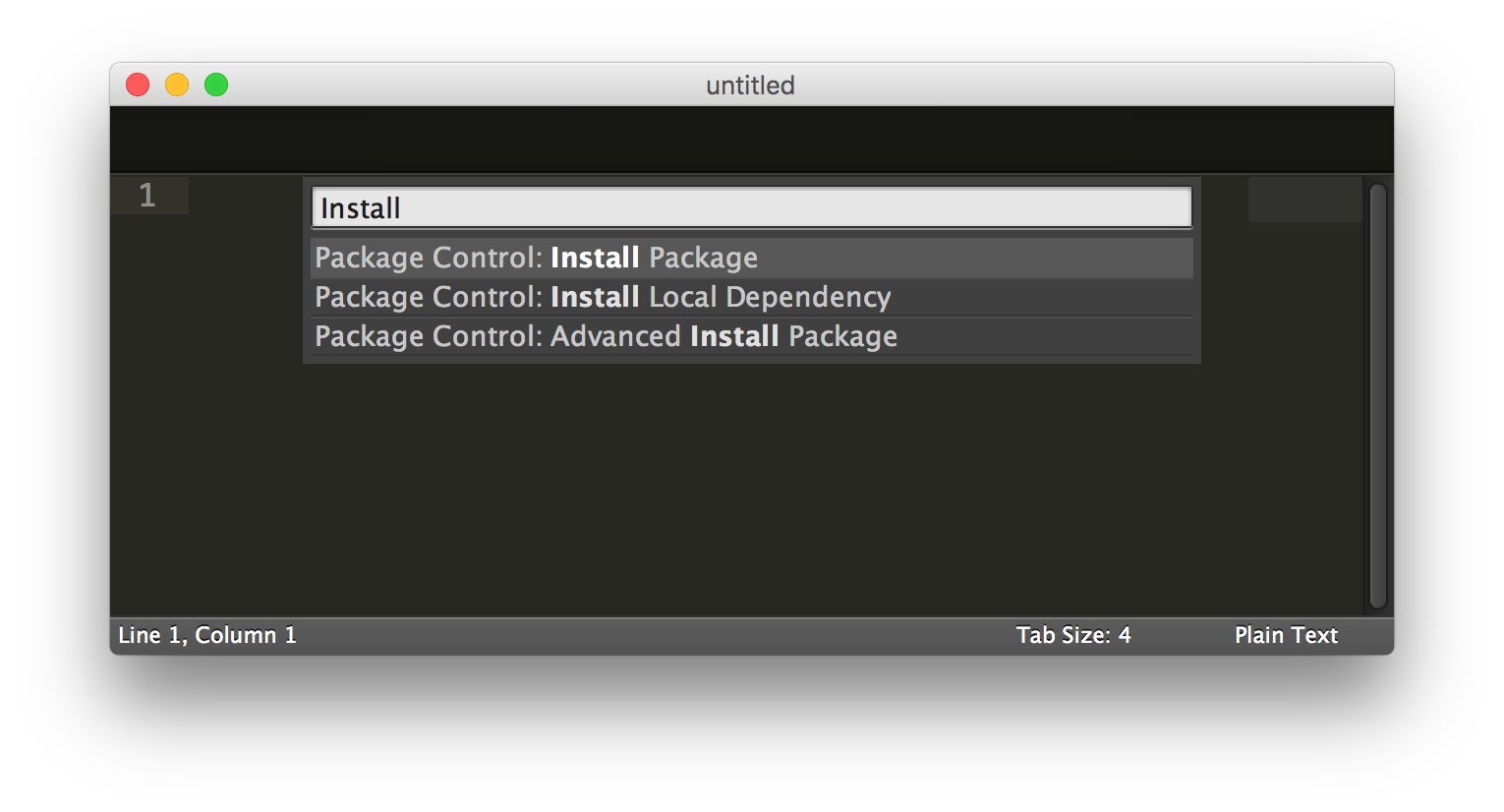

安装完后重启,按command+shift+P唤出命令面板,打开Install Package包管理工具:

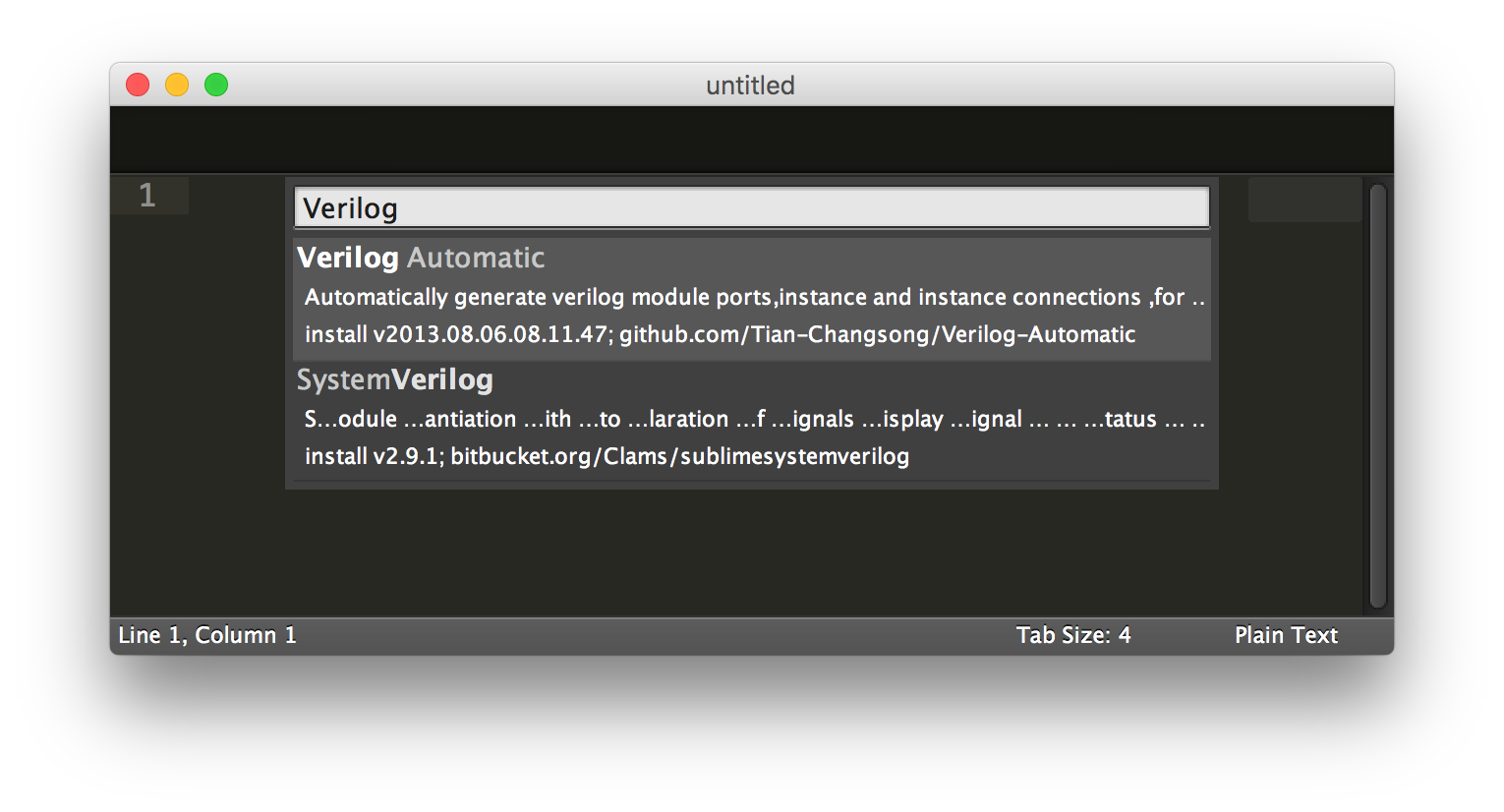

然后查找Verilog,将搜到的自动补全和代码高亮插件装上重启就可以了:

安装Icarus Verilog

Icarus Verilog是Verilog硬件描述语言的实现工具之一。该软件以GNU通用公共许可协议发布,是一个自由软件。它支持Verilog对应的的IEEE 1995、IEEE 2001和IEEE 2005三个不同的版本,并对SystemVerilog的部分内容提供支持。

首先保证已经安装了Homebrew,然后通过brew安装:

brew install icarus-verilog

安装Scansion

Scansion是Mac平台下的一个VCD文件查看工具,可以去http://www.logicpoet.com/downloads/下载其最新版本并安装。

编译仿真

随便新建一个测试文件叫test.v:

1 | module vaddsws( vra, vrb, vrt, sat ); |

再对其新建testbench文件test_tb.v:

1 |

|

注意testbench文件的第二行中include宏是为了引用前一个文件的模块定义,如果在Windows下用ModelSim时把它注释掉就可以了。第13行是为了生成波形文件以便在Scansion里查看。

源码编辑好后执行以下命令编译执行:

iverilog -o test.vvp test_tb.v

./test.vvp

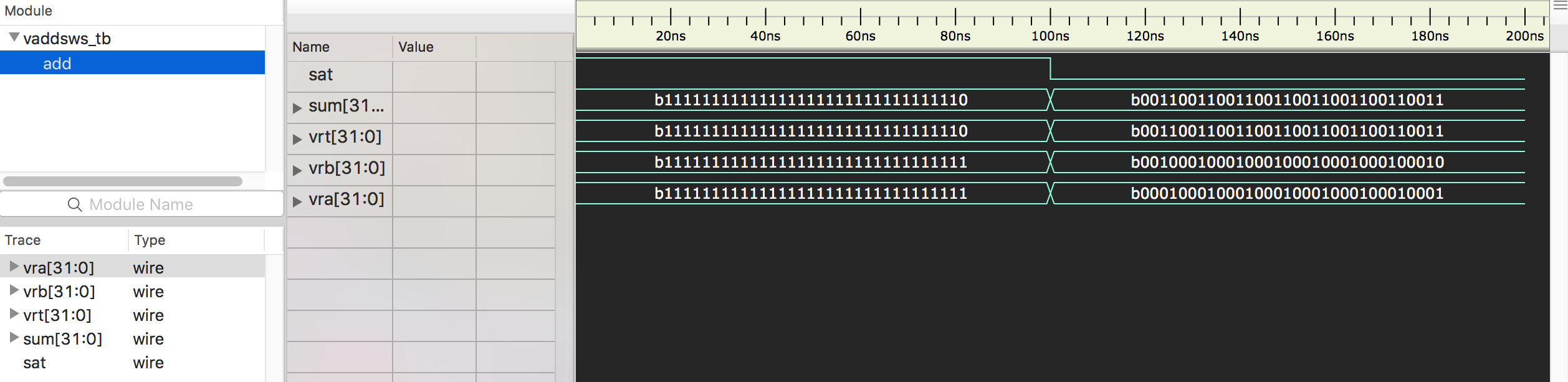

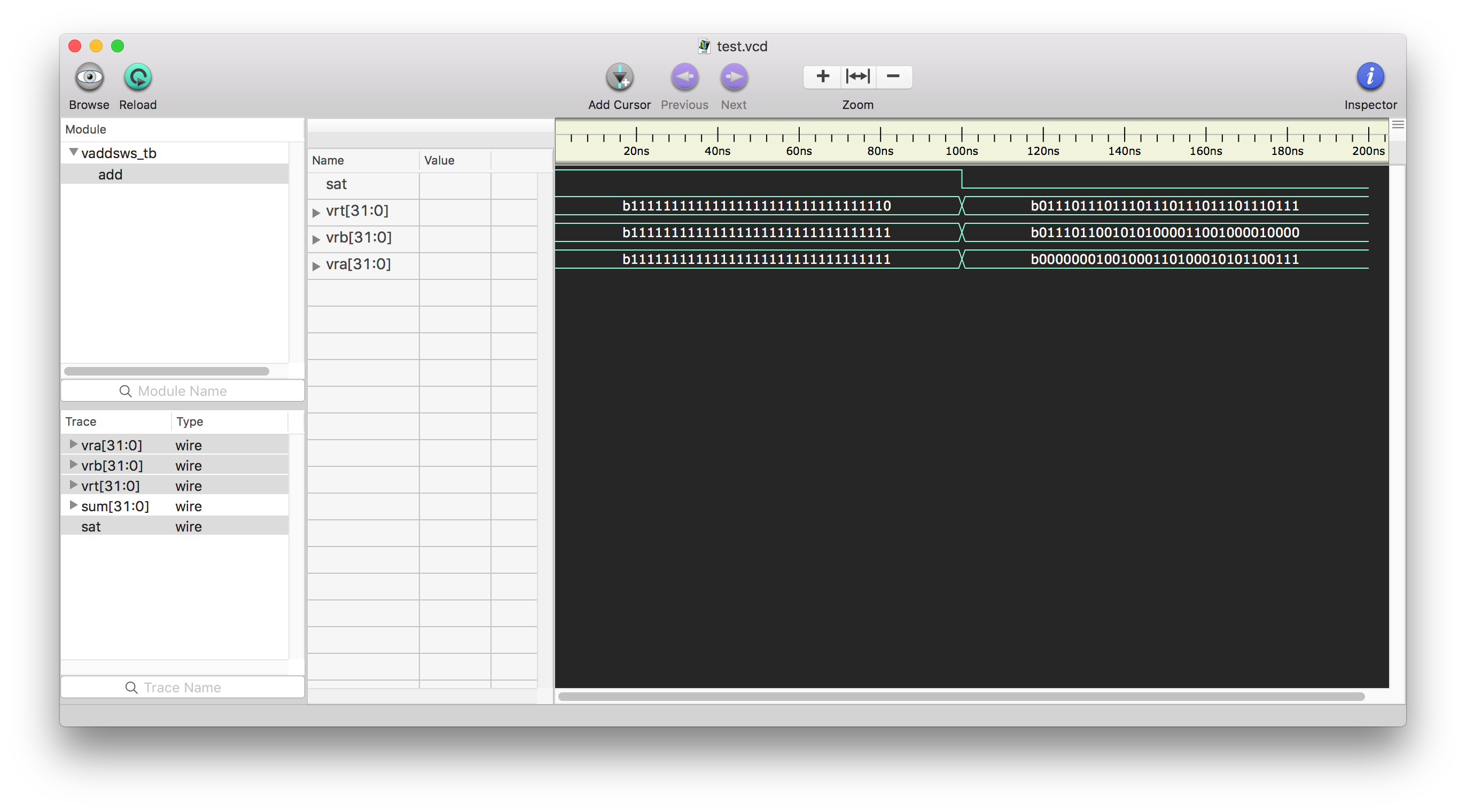

生成vcd格式的波形文件用Scansion打开即可(也可以使用命令open -a Scansion test.vcd):

-

本文作者:

Shintaku

本文链接:

https://www.shintaku.xyz/posts/verilog/

版权声明:

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 Shintaku's Blog 。